XILINX AXI总线学习 |

您所在的位置:网站首页 › xilinx 书籍 › XILINX AXI总线学习 |

XILINX AXI总线学习

|

AXI介绍

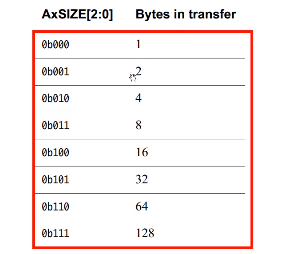

什么是AXI? AXI(高级可扩展接口),是ARM AMBA的一部分; AMBA:高级微控制器总线架构; 是1996年首次引入的一组微控制器总线; 开放的片内互联的总线标准,能在多主机设计中实现多个控制器和 外围设备之间的连接和管理。 AXI三种类型 AXI4(AXI4-Full):用于高性能的存储器映射需求; (存储器映射:主机在对从机进行读写操作时,指定一个目标地址, 这个地址对应系统存储空间的地址,表示对该空间进行读写操作); AXI4-Lite:简化版的AXI4接口 用于低吞吐率存储器映射的通信 AXI4-Stream(ST):用于高速的流数据通信 AXI的优点 生产力 灵活性:AXI4(支持突发256)和AXI4-Lite(1个数据)都属于存储器映射 AXI4-ST不属于存储器映射,它的突发长度不受限制 可获得性 AXI的工作方式 AXI4和AXI-Lite包含5个独立的通道 读地址通道 读数据通道 写地址通道 写数据通道 写响应通道 AXI4:由于读写地址通道是分离的,所以支持双向同时传输;突发长度最大256 AXI4-Lite:和AXI4比较类似,但是不支持突发传输 AXI4-Stream:只有一个单一数据通道,和AXI4的写数据通道比较类似 突发长度不受限制。 AXI InterConnect和AXI SmartConnect 这两个IP核都用于连接单/多个存储器映射的AXI Master和单/多个存储器映射的AXISlave AXI的突发设置 awvalid awready awlen 突发长度+1 awsize 突发字节数 awburst 突发类型 INCR模式 地址自增 WRAP 回环突发

突发字节数

AXI的通道定义 每一个独立的通道都包含一组信息信号、VALID信号和READY信号,用于提供双向的握手机制。 信息源端使用VALID信号表示当前通道地址、数据和控制信息什么时候有效,目的端使用READY信号表示什么时候可以接收信息, 读数据通道和写数据通道都包含一个LAST信号,用于表示传输的最后一个数据。 读数据通道和写数据通道都包含各自的地址通道,地址通道携带了请求所需的地址和信息 读数据通道由从机发送给主机,包含了读数据和读响应的信息,读响应的信号用于表示读 传输是否操作完成; 写数据通道由主机发送给从机,包含了写数据,然后通过WSTRB信号表示当前数据的 哪个字节有效 写响应通道由从机发给主机,包含了写响应信号,用于表示当前写操作是否完成。 握手机制 所有的五个通道都是通过相同的VALID/READY握手处理来传输地址、数据和控制信息 双向握手的机制意味着主机和从机之间传输数据时,都可以控制传输的速率 只有当VALID和READY同时为高电平时,传输才会发生。 AX4-Lite 适用于当不需要AXI4完整功能的时候,一些简单的控制寄存器的读写

|

【本文地址】

今日新闻 |

推荐新闻 |